# HOW TO PROGRAM AND INTERFACE THE 6800

BY ANDREW C. STAUGAARD, JR.

#### The Blacksburg Continuing Education™ Series

The Blacksburg Continuing Education Series<sup>TM</sup> of books provide a Laboratory—or experimentoriented approach to electronic topics. Present and forthcoming titles in this series include:

- Advanced 6502 Interfacing

- Analog Instrumentation Fundamentals

- Apple Assembly Language

- Apple Interfacing

- Basic Business Software

- BASIC Programmer's Notebook

- Circiut Design Programs for the Apple II

- Circuit Design Programs for the TRS-80

- Computer Assisted Home Energy Management

- Design of Active Filters, With Experiments

- Design of Op-Amp Circuits, With Experiments

- Design of Phase-Locked Loop Circuits, With Experiments

- Design of Transistor Circuits, With Experiments

- 8080/8085 Software Design (2 Volumes)

- 8085A Cookbook

- Electronic Music Circuits

- 555 Timer Applications Sourcebook, With Experiments

- Guide to CMOS Basics, Circuits, & Experiments

- How to Program and Interface the 6800

- Introduction to Electronic Speech Synthesis

- Introduction to FORTH

- Microcomputer—Analog Converter Software and Hardware Interfacing

- Microcomputer Data-Base Management

- Microcomputer Design and Maintenance

- Microcomputer Interfacing With the 8255 PPI Chip

- NCR Basic Electronics Course, With Experiments

- NCR EDP Concepts Course

- PET Interfacing

- Programming and Interfacing the 6502, With Experiments

- Real Time Control With the TRS-80

- 16-Bit Microprocessors

- 6502 Software Design

- 6801, 68701, and 6803 Microcomputer Programming and Interfacing

- The 68000: Principles and Programming

- 6809 Microcomputer Programming & Interfacing, With Experiments

- STD Bus Interfacing

- TEA: An 8080/8085 Co-Resident Editor/Assembler

- TRS-80 Assembly Language Made Simple

- TRS-80 Color Computer Interfacing

- TRS-80 Interfacing (2 Volumes)

- TRS-80 More Than BASIC

In most cases, these books provide both text material and experiments, which permit one to demonstrate and explore the concepts that are covered in the book. These books remain among the very few that provide step-by-step instructions concerning how to learn basic electronic concepts, wire actual circuits, test microcomputer interfaces, and program computers based on popular microprocessor chips. We have found that the books are very useful to the electronic novice who desires to join the "electronics revolution," with minimum time and effort.

Jonathan A. Titus, Christopher A. Titus, and David G. Larsen "The Blacksburg Group"

## How to Program and Interface the 6800

by Andrew C. Staugaard, Jr. Copyright © 1980 by Andrew C. Staugaard, Jr.

#### FIRST EDITION FOURTH PRINTING-1982

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21684-1 Library of Congress Catalog Card Number: 80-50050

Printed in the United States of America.

#### **Preface**

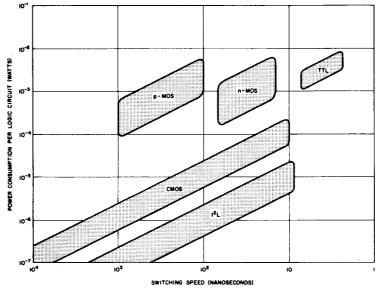

In the past few years, we have experienced a revolution in electronic computer technology that began with the introduction of the first microprocessor in 1971. This revolution was made possible by an integrated-circuit technology called large scale integration (LSI), which is the ability to pack thousands of transistor devices within a small silicon "chip." As a result of this technology, we have seen circuit complexity and capability double each year with this pace expected to continue for the foreseeable future by the introduction of circuits utilizing very-large scale integration (VLSI) and superlarge scale integration (SLSI). These new integration technologies have not only increased circuit capabilities, but have surprisingly and dramatically reduced circuit costs. Products such as appliances, instrumentation, toys, games, etc., which could never possess a computer "intelligence" because the cost was prohibitive, are now being marketed with microcomputer control at minimum cost. One of the first microprocessor applications was the electronic calculator industry. In the past years, we have seen calculator capabilities go up and cost come down. Not only are microprocessors finding widespread use in these products, but they have also spawned a hobby computer market. Full computer systems are now available for less than half the price of a new automobile-something unheard of 10 years ago.

After the introduction of the first microprocessor chip by the Intel Corporation, many semiconductor companies introduced their own microprocessors. Three leading chips emerged: the Motorola 6800, Intel 8080, and Zilog Z-80. Each of these is an 8-bit central processing unit (CPU) that requires external memory and i/o circuitry to function as a microcomputer. However, we are now witnessing a surge of "computer-on-a-chip" devices that contain all the logic, memory, and i/o capability for a small microcomputer in one integrated circuit package.

Motorola, at the time of this writing, is the only company that has developed these new chips around its standard 6800 architecture.

The 6800 "family" now ranges from an advanced microprocessor, the 6809, to a *complete* single-chip microcomputer, the 6801. This broad range of software compatibility, which is not currently available within the 8080 and Z-80 chip families, is highly desirable since it permits one to meet a wide variety of application requirements. This was one of the important reasons for the decision by General Motors and the Ford Motor Co. to incorporate the 6800 family of microprocessors/microcomputers into their new cars.

In this book, we will provide you with an introduction to the world of microprocessors/microcomputers via the Motorola 6800. It begins with microprocessor/microcomputer concepts and, therefore, assumes the reader has a basic understanding of number systems and digital electronic concepts. However, this prerequisite material is presented in Appendix A and Appendix B for the reader who might need some "brushing-up" or is not familiar with these concepts. The first chapters of the book discuss the 6800 internal structure, instruction set, and programming techniques. The final chapters are devoted to the 6800 hardware and interfacing techniques.

The book is meant to be a tutorial type of text for an introduction to the 6800 or microprocessors/microcomputers in general. Review questions and answers are provided after each chapter. In addition, there are over 30 "hands-on" experiments provided throughout the text that demonstrate "real-world" applications. The experiments are written around the Heath ET3400 microcomputer learning system and the Motorola MEK6800D2 evaluation kit. Applications are stressed throughout the text and are especially evident in the chapters on interfacing where the reader learns how to construct a minimum workable 6800 system and interface that system to switches, keyboards, displays, digital-to-analog converters, and analog-to-digital converters.

Finally, I would like to express my appreciation to Dave Larsen of Virginia Polytechnic Institute and State University whose encouragement to write on the Motorola chip line led to this book and to Jon Titus of Tychon, Inc., whose many suggestions have contributed to the final product. In addition, I must thank my wife, Janet, for her talent with a typewriter and to one of my students, Sandy Trentini, whose talent at the drawing board is evident in most of the text illustrations.

ANDREW C. STAUGAARD, JR.

#### **Contents**

#### **CHAPTER 1**

| FUNDAMENTAL MICROPROCESSOR CONCEPTS                                                                                                                 | 9  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Introduction — Objectives — Microprocessor/Microcomputer Basics — Basic 6800 Chip Structure—6800 Fetch and Execute—Review Questions—Answers         |    |

| CHAPTER 2                                                                                                                                           |    |

| HEATH ET3400 AND MOTOROLA MEK6800 MICROCOMPUTER LEARNING SYSTEMS                                                                                    | 27 |

| Introduction—Objectives—Heath ET3400 Microcomputer Learning System—Motorola MEK6800D2 Evaluation Kit—Experiment Instructions and Format—Experiments |    |

| CHAPTER 3                                                                                                                                           |    |

| 6800 Arithmetic, Logic, and Data-Handling Instructions .                                                                                            | 52 |

| Introduction—Objectives—6800 Data Transfer—6800 Arithmetic Instructions—6800 Logic Instructions—Review Questions—Answers—Experiments                |    |

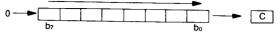

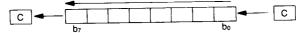

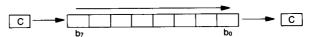

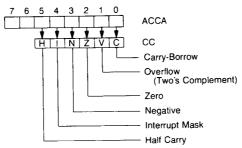

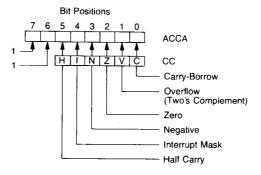

| Condition Code Register and Data Shifting/Comparing/Testing                                                                                                                                                                    | 84  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction—Objectives—Condition Code Register—Data Shifting, Rotating, Comparing, and Testing—Review Questions—Answers—Experiments                                                                                           |     |

| CHAPTER 5                                                                                                                                                                                                                      |     |

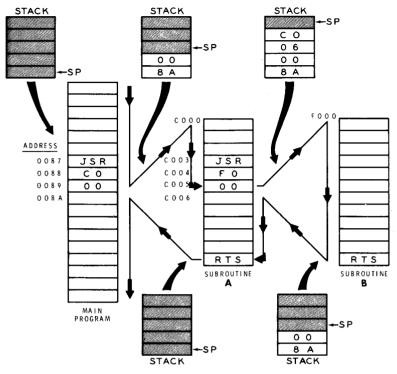

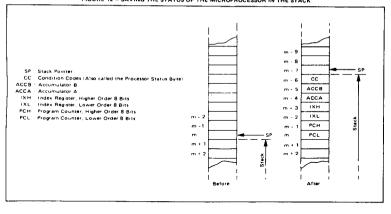

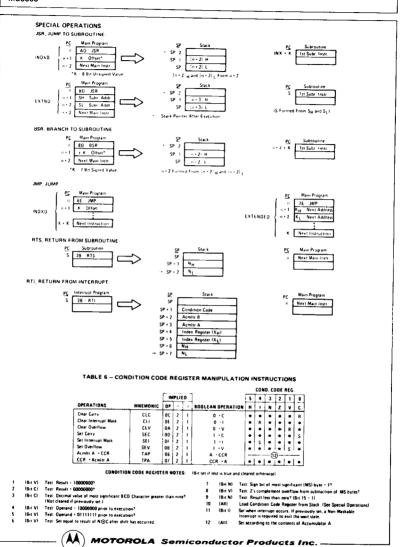

| 6800 Branching, Indexing, and Stacks                                                                                                                                                                                           | 113 |

| Introduction — Objectives — Branching — Branch Instructions — Index Register and Addressing—Stacks and Stack Pointer—Subroutines—Review Questions—Answers—Experiments                                                          |     |

| CHAPTER 6                                                                                                                                                                                                                      |     |

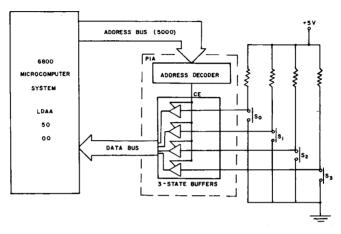

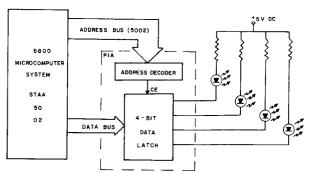

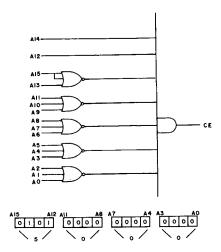

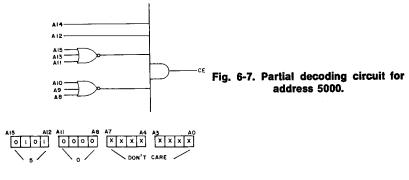

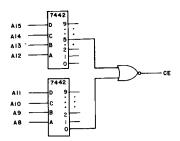

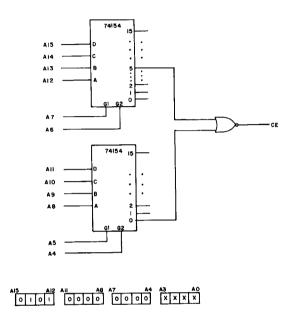

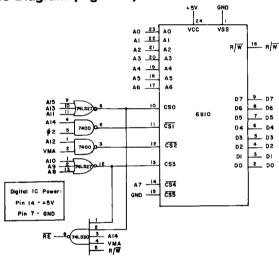

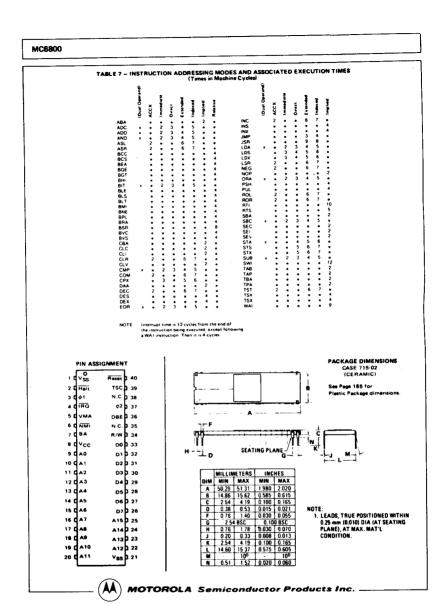

| 6800 Input/Output                                                                                                                                                                                                              | 144 |

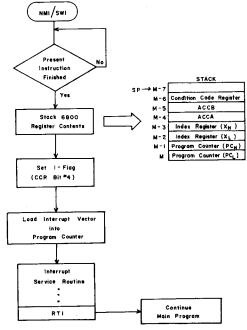

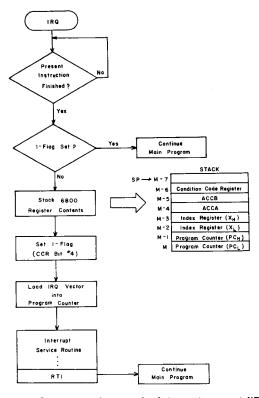

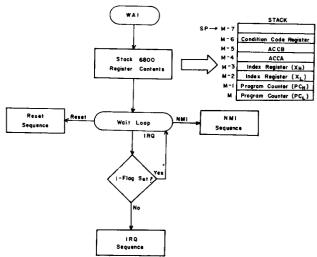

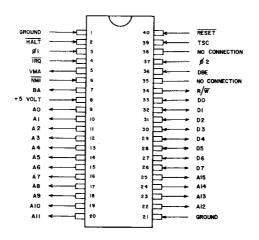

| Introduction—Objectives—General I/O Concepts—Decoding—I/O Techniques—6800 Interrupts—Pin Assignments—Review Questions—Answers—Experiments                                                                                      |     |

| CHAPTER 7                                                                                                                                                                                                                      |     |

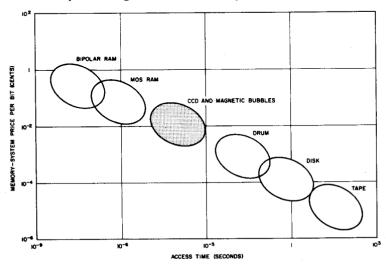

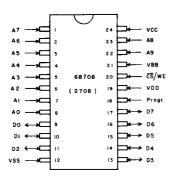

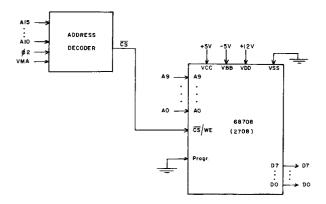

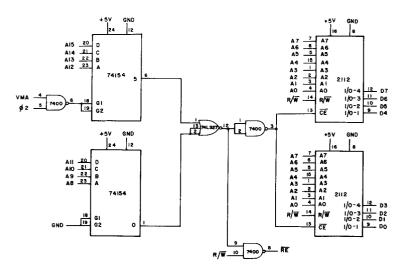

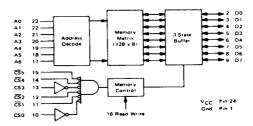

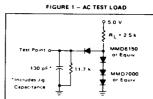

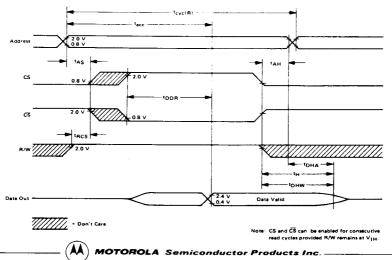

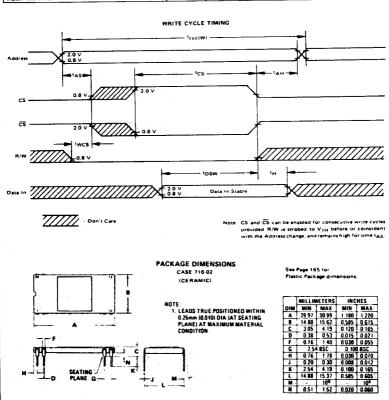

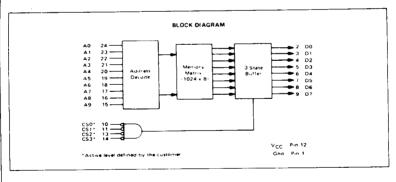

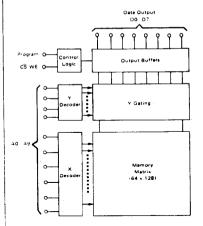

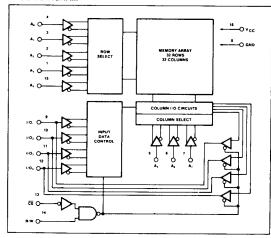

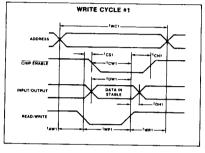

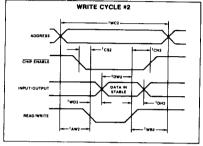

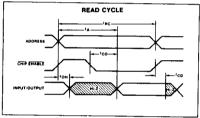

| Interfacing With Memory                                                                                                                                                                                                        | 178 |

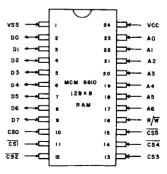

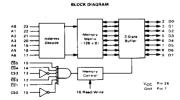

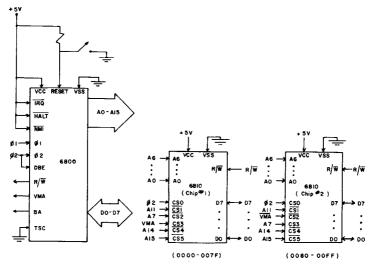

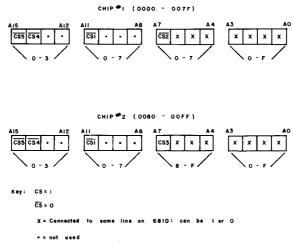

| Introduction — Objectives — Memory Technology — Interfacing With Read/Write Memory—MCM6810 R/W Memory—2112 R/W Memory—Interfacing With Read-Only Memory (ROM)—MCM68708 (Intel 2708) EPROM—Review Questions—Answers—Experiments |     |

| CHAPTER 8                                                                                                                                                                                                                      |     |

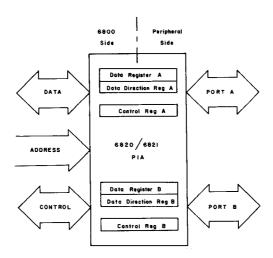

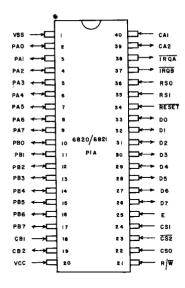

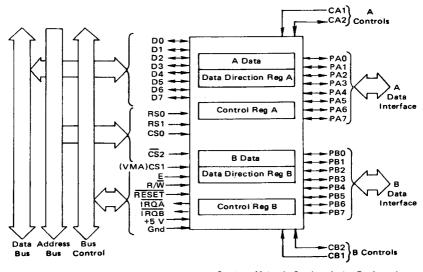

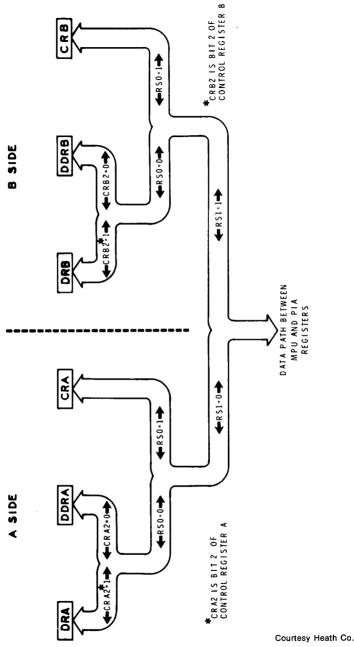

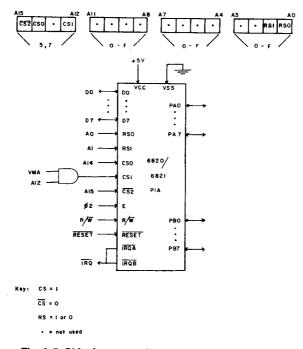

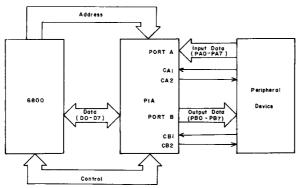

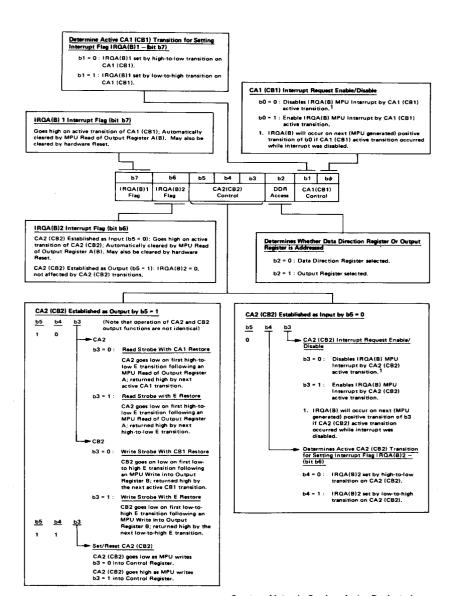

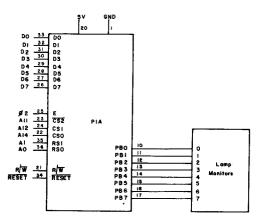

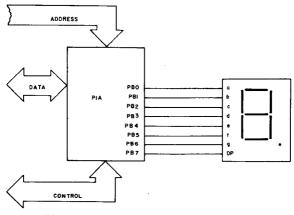

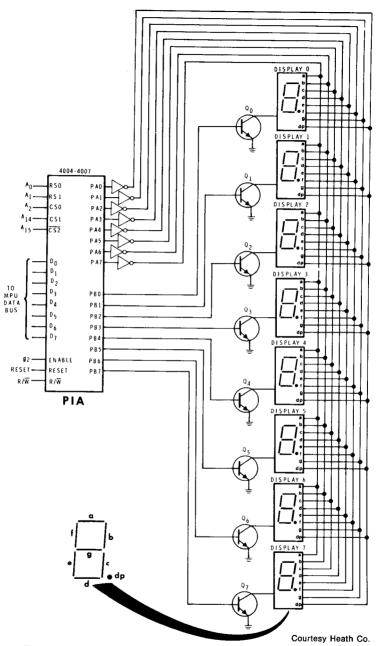

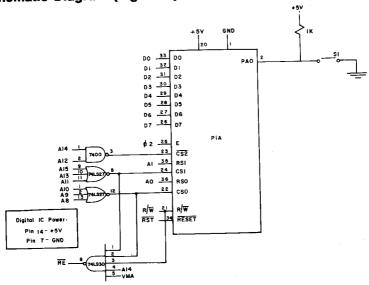

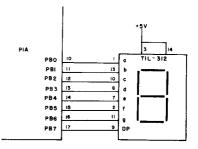

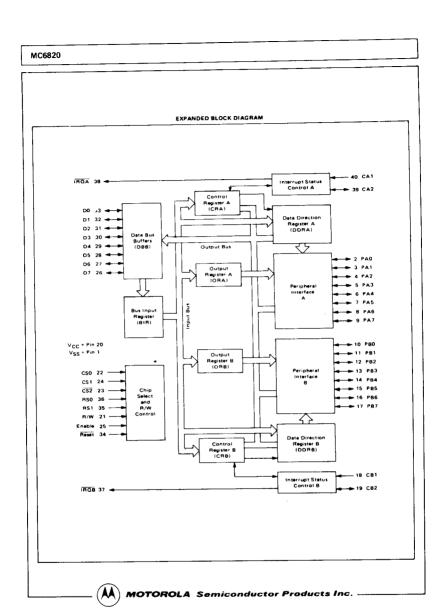

| THE 6820/6821 PERIPHERAL INTERFACE ADAPTER                                                                                                                                                                                     | 208 |

| Introduction—Objectives—6821 Functional Description—PIA Interfacing and Addressing—PIA Initialization and Servicing—Review Questions—Answers—Experiments                                                                       |     |

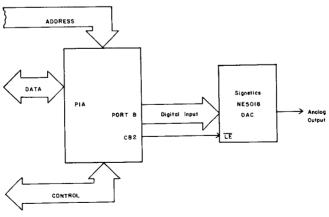

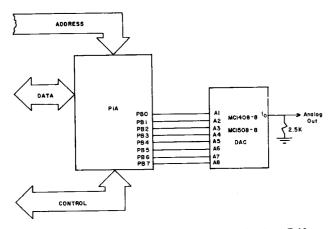

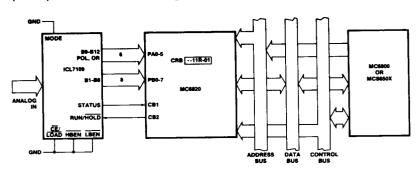

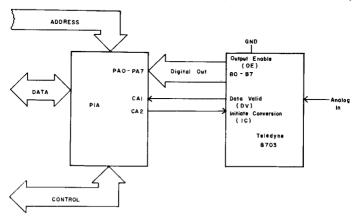

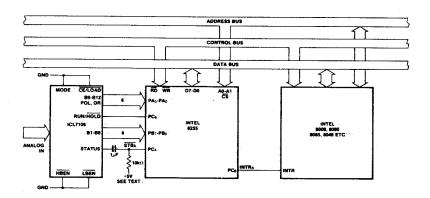

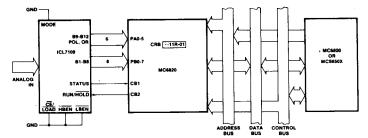

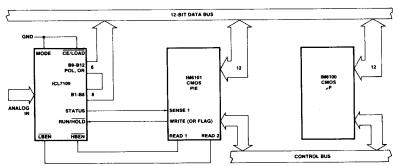

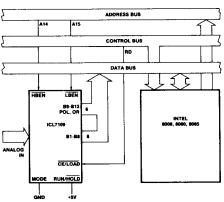

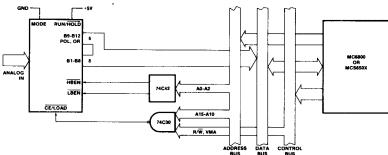

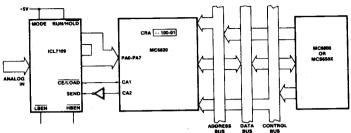

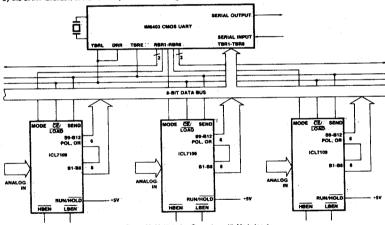

| 6800 System Interfacing                                                                                                                                                                                                                             | 240 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Introduction — Objectives — Interfacing With Switches — Interfacing With Keyboards — Interfacing With Displays — Interfacing With Digital-to-Analog Converters — Interfacing With Analog-to-Digital Converters—Review Questions—Answers—Experiments |     |  |  |

| APPENDIX A                                                                                                                                                                                                                                          |     |  |  |

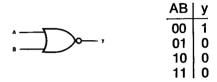

| DIGITAL REVIEW                                                                                                                                                                                                                                      | 279 |  |  |

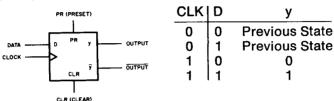

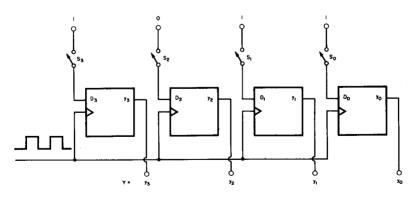

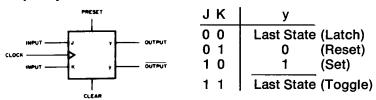

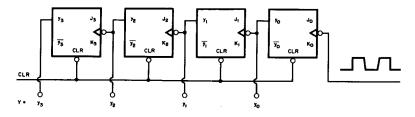

| Basic Logic Gates—Flip-Flops                                                                                                                                                                                                                        |     |  |  |

| APPENDIX B                                                                                                                                                                                                                                          |     |  |  |

| Number Systems and Computer Arithmetic                                                                                                                                                                                                              | 285 |  |  |

| Number Systems—Digital Computer Arithmetic                                                                                                                                                                                                          |     |  |  |

| APPENDIX C                                                                                                                                                                                                                                          |     |  |  |

| 6800 Instruction Set                                                                                                                                                                                                                                | 297 |  |  |

| Symbol Definitions and Nomenclature—Executable Instructions                                                                                                                                                                                         |     |  |  |

| APPENDIX D                                                                                                                                                                                                                                          |     |  |  |

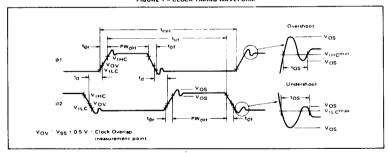

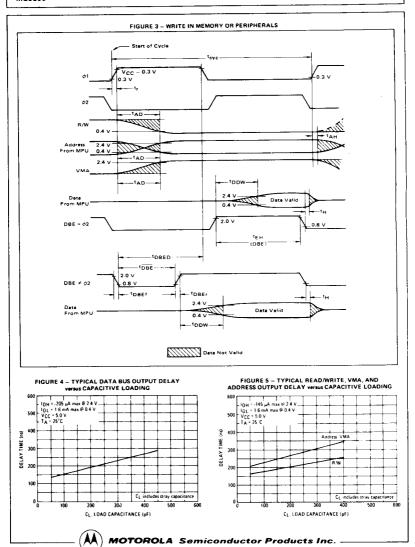

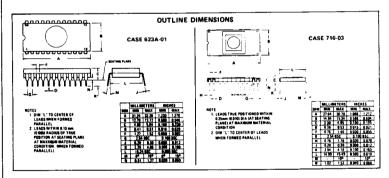

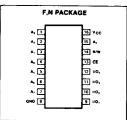

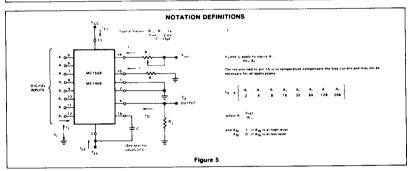

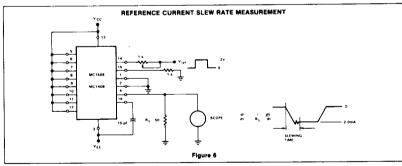

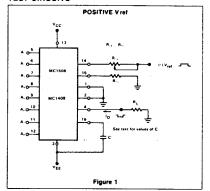

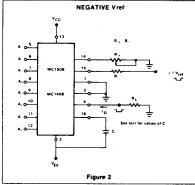

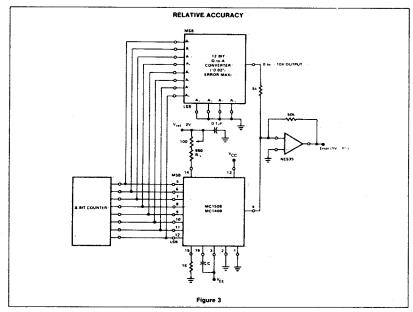

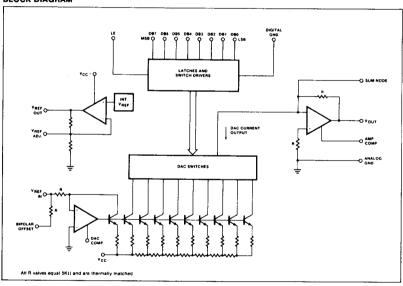

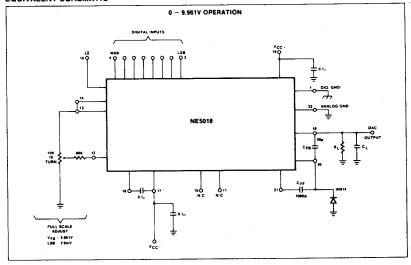

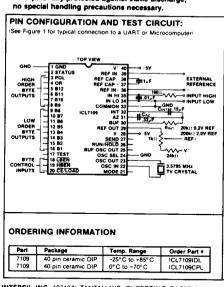

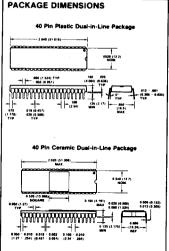

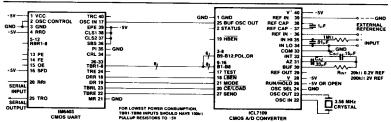

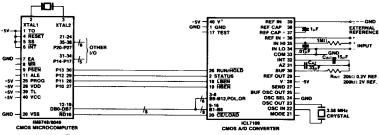

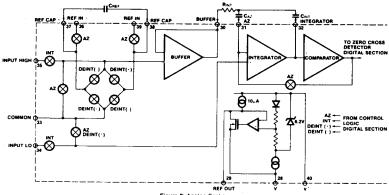

| Specification Sheets                                                                                                                                                                                                                                | 340 |  |  |

| MC6800/MC6800C—MCM6810A/MCM6810C—MC6820/MC6820C<br>—MCM6830A—MCM68708/MCM68A708—2112—MC1508/MC1408<br>—NE5018—ICL7109                                                                                                                               |     |  |  |

| INDEX                                                                                                                                                                                                                                               | 411 |  |  |

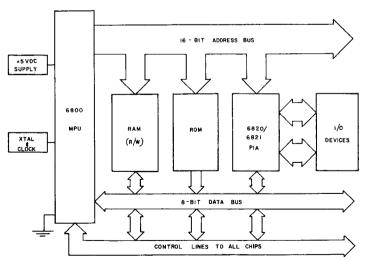

### Fundamental Microprocessor Concepts

#### INTRODUCTION

In this chapter we will begin by discussing the fundamental differences between a microprocessor chip, a microcomputer chip, and a microcomputer system. This will then lead to a discussion of chip families, specifically the Motorola 6800 family. Once the decision to purchase a particular microprocessor or microcomputer chip is made, the purchaser is really committed to a chip family. The family will consist of all the external support chips required to make a workable system. Such support chips include read/write memory, read-only memory, peripheral interface chips, peripheral controllers, etc. If a manufacturer maintains family compatibility for future chip design, even the newer-generation microprocessors and microcomputer chips can be part of the same basic family. This is the case with the Motorola 6800 chip line. All of the newer-generation chips such as the 6802, 6809, and 6801 are software, and to some extent hardware. compatible with the 6800. Therefore, we include them as part of the 6800 family.

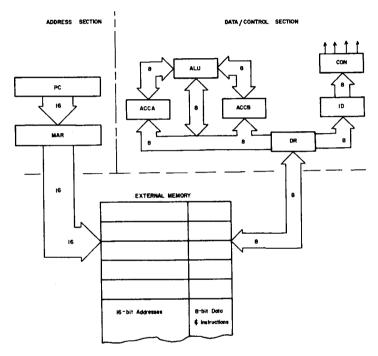

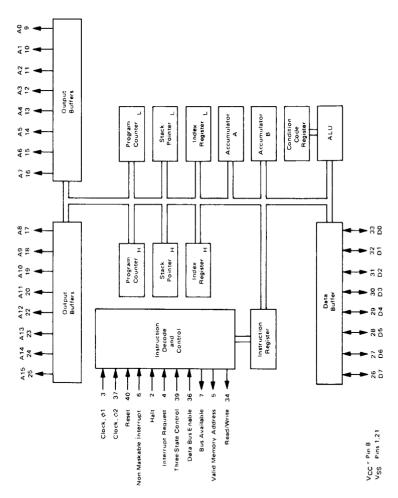

We will then take a closer look at the 6800 chip which can be divided into three functional regions: address, data, and control. We will discuss the internal registers that make up each functional region. This will be the beginning 6800 structure (architecture) which will be completed in Chapter 3. You will become familiar with the 6800 instruction format. A simple program will then be

written to add two numbers and the program execution will be traced through the internal structure of the 6800.

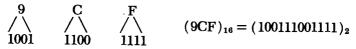

Finally, in order to understand digital computers, it is necessary to know the binary number system. Since the learning systems used with the experiments employ the hexadecimal (hex) number system and all of the programs will be written in hex, it is especially important to understand this number system as well as how to convert between hex and other number systems such as binary and decimal. It might be helpful to review number systems in Appendix B prior to reading this chapter.

#### **OBJECTIVES**

At the end of this chapter you will be able to do the following:

- Understand the difference between a microprocessor and microcomputer.

- Know some microprocessor chip families and microcomputer systems and their applications.

- Distinguish between read/write and read-only memory.

- Understand the basic internal structure of the 6800.

- Distinguish between microcomputer instructions written in binary code, hexadecimal code, or mnemonic code.

- Understand and trace a simple program through the 6800 chip.

#### MICROPROCESSOR/MICROCOMPUTER BASICS

Let us start by making a distinction between the terms microprocessor and microcomputer. A microprocessor is usually only a single integrated circuit, or "chip," and it is generally thought of as a Central Processing Unit (CPU). It does not contain any permanent memory or convenient input/output (i/o) features. Many of these chips do not include a clock for the timing of operations and none of them include a power supply. The first- and second-generation chips such as the Motorola 6800 and 6802; the Intel 8008, 8080, and 8085; and the Zilog Z-80 are truly microprocessors. They are the result of Large Scale Integration (LSI) which can integrate 500 to 10,000 transistors and associated components on a 100-mil × 100-mil silicon chip. These chips are not "stand-alone" computers and may require anywhere from 3 to 300 additional digital chips and i/o devices to achieve a workable system, depending on the application. However, these microprocessor chips sell for under \$20.00 and represent as much computing power as many of the larger computers of the mid-1960s. Present applications of these devices are calculators, tv games, "smart" toys, appliances, home and small-business computing systems, industrial process controls, and automobiles. The largest future applications are seen to be in homes, automobiles, appliances, and industrial controls. Because of the low cost of these devices, almost any mechanical or electrical product has the potential of utilizing a programmed intelligence.

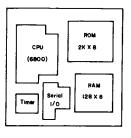

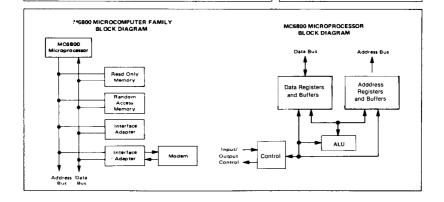

A microcomputer, on the other hand, is virtually a total computer system. It can be as large or small as the application requires. The microcomputer can be broken down into two categories: the microcomputer chip and microcomputer system. The microcomputer chip is a result of third-generation technology that utilizes VLSI (Very-Large Scale Integration) which integrates from 10,000 to 50,000 transistors and associated components per chip. This 40-pin chip will typically contain a small amount of read-only and read/write memory, a clock, possibly a serial communications interface capability or an internal analog-to-digital converter, and other i/o features. The Motorola 6801 and Intel 8748 are products of this technology. These chips are "stand-alone" computers for many small applications, such as appliances and industrial controls. They will be used for future applications essentially in the same manner as the microprocessor chip. The Motorola 6801 microcomputer chip layout is shown in Fig. 1-1.

Fig. 1-1. Motorola 6801 microcomputer chip layout.

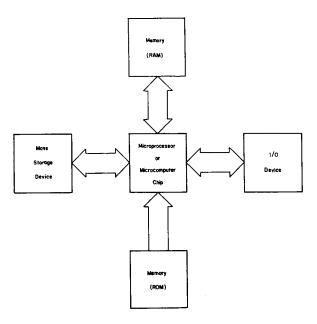

The second category of microcomputers is the microcomputer system. This system is built around the microprocessor or microcomputer chip. Such systems usually contain the following, external to the chip itself.

- 1. Read-Only Memory (ROM) for operation control.

- 2. Read/Write (R/W) memory for data storage.

- 3. CRT and keyboard for convenient user input/output.

- 4. Floppy disk or cassette recorder for mass data storage.

Fig. 1-2. Microcomputer system block diagram.

Examples of such systems are the Radio Shack TRS-80, Heathkit H-8, IMSAI 8080, Altair 8800, and Cromemco Z-2. These systems are relatively inexpensive and rival many minicomputers in their capabilities. They can be used for industrial process control, data acquisition, and personal and small business computing. They are also a very popular hobby item. A microcomputer system block diagram is shown in Fig. 1-2. Note that the microprocessor/microcomputer chip is at the "heart" of the system.

Before we begin with a detailed discussion of the 6800 chip, let us look at some microprocessor and microcomputer chip families.

Manufacturers of microprocessor chips, such as Motorola, Intel, Zilog, and RCA, have each marketed a complete series of external chips that can be used with their microprocessor. Remember, the beauty of a microcomputer system is that it can be as large or as small as the application requires. Therefore, once a particular microprocessor is purchased, almost any number of chips within the family of that microprocessor can be added to obtain the desired system. All chips within a family are compatible, which means that they typically use the same supply voltages, have the same size data words, etc. The 6801 we referred to earlier is considered part of the 6800

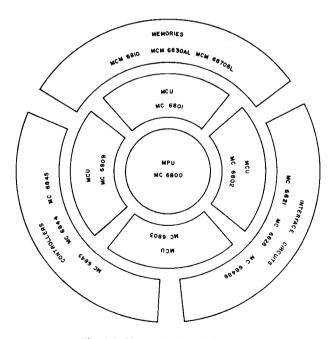

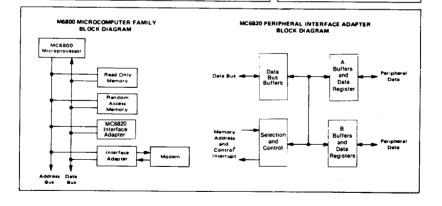

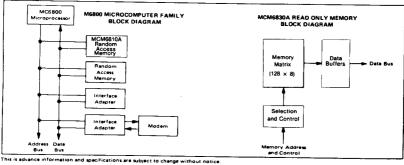

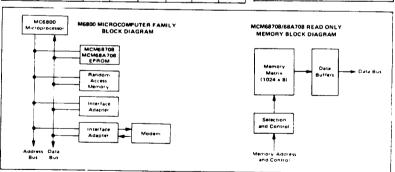

chip family since it uses the 6800 as its Central Processing Unit (CPU). See Fig. 1-1. The same is true of the Motorola 6802, 6803, and 6809 microcomputer chips. We intend to study the 6800 in detail because it is the basic hardware and software model for almost all of Motorola's chip line. All of the Motorola microcomputer chips, such as the 6801, 6802, 6803, and 6809, utilize the 6800 as their CPU and many future Motorola chips will be software and hardware compatible with the 6800. Fig. 1-3 shows the 6800 chip family. There are many chips within the family other than the ones indicated in Fig. 1-3. For a complete listing and description of all the 6800 family, consult The Complete Motorola Microcomputer Data Library, available from Motorola Semiconductor Products, Inc., Box 20912, Phoenix, Arizona 85036. We will cover some of these chips in more detail when we discuss interfacing.

#### **BASIC 6800 CHIP STRUCTURE**

We will begin with a description of only those functional parts of the 6800 that will permit us to program simple operations. Then,

Fig. 1-3. Motorola 6800 chip family.

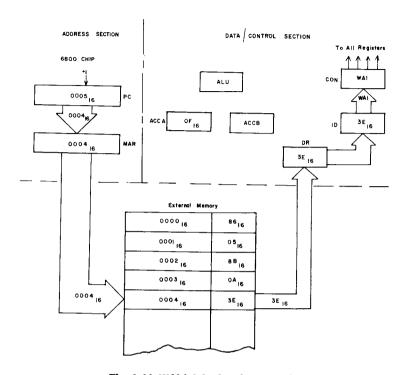

later on, we will complete the 6800 architecture with the addition of some special functions to make the 6800 a very powerful processing unit. Fig. 1-4 represents the beginning of our 6800 structure.

First, note that the chip is divided into two distinct sections, address and data/control. On the surface it would seem that these sections are unconnected and unrelated. However, both sections are connected to an external memory. The address section is used to

Fig. 1-4. 6800 functional chip structure.

fetch program instructions and data from memory and the data/control section is used to interpret these instructions and execute the program commands. Therefore, the sections are related and interact with each other via an external memory.

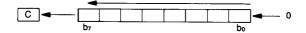

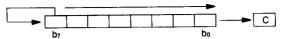

Second, note that broad arrows connect the various blocks. These are internal buses (conductor paths) that transmit binary information from one area to another. The arrow indicates the direction of information flow. Note that some of the buses are bidirectional. The number within the bus indicates the size of the bus in binary bits. Therefore, by observation, the address section utilizes 16-bit buses

while the data/control section uses 8-bit buses. Now let us look at each functional block in more detail.

#### **Program Counter**

The Program Counter (PC) is simply a 16-bit binary counter. The PC is capable of counting from 0000 0000 0000 0000<sub>2</sub> to 1111 1111 1111 1111<sub>2</sub> or 0000<sub>16</sub> to FFFF<sub>16</sub>. When the counter is clocked by CON, it will be incremented by one binary digit. The count in the PC will represent an address in memory. In fact, it is always the memory address of the *next* program instruction to be performed.

#### **Memory Address Register**

The Memory Address Register (MAR) is a 16-bit storage register. It receives a 16-bit memory address from the PC. It will then pass the address to the external memory to "fetch" the next program instruction to be performed.

#### **External Memory**

This memory is external to the 6800 chip. It is a Random-Access Memory (RAM). A RAM can be thought of as a Read/Write (R/W) memory, i.e., information can be read from the memory and information can also be written into the memory. Each location in memory contains an 8-bit word; therefore, all information in the memory is ordered in 8-bit blocks, or bytes, as shown in Fig. 1-4. This is why the 6800 data bus in Fig. 1-4 is an 8-bit bus.

Each byte of information must have an address so that it can be located. The address is a 16-bit (2-byte) word and this is the reason that the 6800 address bus is a 16-bit bus. Since our address is a 16-bit word, there are 2<sup>16</sup> possible addresses. Therefore, we say that the 6800 is capable of addressing 65,536 locations in memory. More will be said about memory later.

#### **Data Register**

The Data Register (DR) is an 8-bit temporary storage register which receives 8-bit information from memory. If the 8-bit memory information is a program instruction, the DR will pass it to the instruction decoder. If the information is to be processed, rather than used to indicate an operation, the DR will pass it to one of the accumulators or the Arithmetic Logic Unit (alu), depending upon the previous program instruction command. The DR directs the information and is, therefore, sometimes referred to as a Data Direction Register (DDR).

#### Instruction Decoder

The Instruction Decoder (ID) is exactly what the name implies. It decodes, or interprets, 8-bit instructions received from memory. It will then direct the chip to "execute" the instructions through the controller/sequencer.

#### Controller/Sequencer

The CONtroller/Sequencer (CON) receives the decoded instructions from the instruction decoder and enables and disables the other parts of the chip to carry out these instructions. Therefore, it controls and sequences all of the operations within the chip.

#### **Accumulators**

The 6800 contains two accumulators, ACCumulator A and ACCumulator B (ACCA and ACCB). These are 8-bit storage registers that are used to hold operands before they are used in an operation and are also used to hold the results of operations after they have been performed. Operands are data to be used as part of an operation.

#### Example 1-1: Use of Instructions and Operands

$$\begin{array}{c} \text{ADD} & \longrightarrow & \text{Instruction} \\ 2 & \longrightarrow & \text{Operand} \end{array}$$

The operand is the number used in the operation. In this case, we are adding two. ADD is the instruction, while 2 is the operand.

#### **Arithmetic Logic Unit**

The alu is the heart of the 6800 microprocessor chip. It performs all of the arithmetic and logic operations. The results of these operations are stored in one of the accumulators. Typical operations are adding, subtracting, ANDing, ORING, or XORING.

#### 6800 FETCH AND EXECUTE

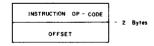

Before we trace a simple operation through the chip, let us look at a typical instruction format. Instructions in the 6800 can be one, two, or three bytes in length. As shown in Example 1-2, the first byte is always the command. The second byte can be a memory address or data. The third byte is always part of a memory address or a second data byte. Some commands require a second or third byte while others do not.

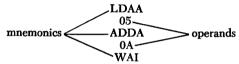

In writing a series of instructions, the mnemonic of the command is listed then the second and third bytes in hex are shown, if they are required. Since hexadecimal is used as a standard number sys-

#### Example 1-2: 6800 instruction Format

| 1st byte | 8-bit command               |

|----------|-----------------------------|

| 2nd byte | address or data             |

| 3rd byte | optional address<br>or data |

NOTE: Since our command byte is eight bits, there are 2<sup>s</sup>, or 256, different commands possible with an 8-bit chip such as the 6800.

tem, all numbers in the program listings will be hex unless otherwise indicated with a subscript.

A mnemonic is simply a representation for a command that is easily understood and remembered by the programmer. An op code is the 8-bit binary or 2-digit hex representation for the mnemonic which resides in memory.

Now let us look at the following program listing.

Example 1-3: 6800 Sample Program Listing

The first command is to LoaD Accumulator A with 5. The second command tells the computer to ADD 0A to the contents of accumulator A. The third instruction tells the computer to WAIt or halt its operation.

The second bytes of the first two instructions are operands and *not* addresses; neither of the instructions require a third byte. In fact, the WAI instruction does not require a second or third byte.

Note that in the preceding description of the program, we have capitalized each letter that forms the mnemonic of the instruction. This will be done throughout the text when new instruction mnemonics are introduced.

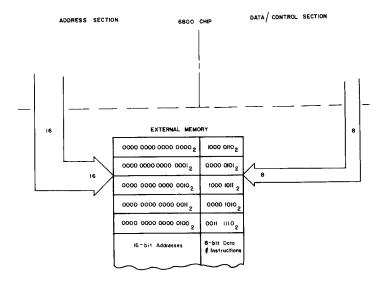

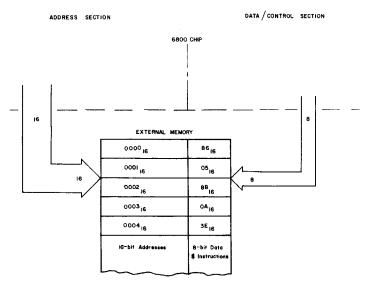

Once the program is loaded into memory, it is ready to go. The memory structure for this program is represented by Fig. 1-5 which is the actual binary memory structure. However, for ease of diagramming, hexadecimal is used to represent memory addresses and information as shown in Fig. 1-6. Note that the LDDA, ADDA and WAI instructions are represented by their respective op codes.

Now, we will trace the program through the 6800 chip and external memory. Our explanation will use Figs. 1-7 through 1-11.

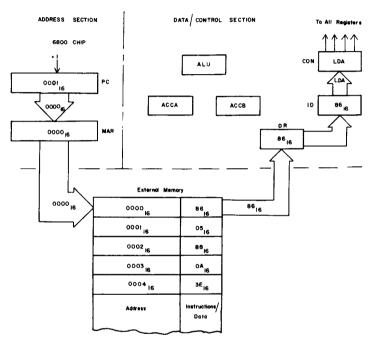

#### Figure 1-7

The first instruction (LDAA) is fetched and decoded.

Fig. 1-5. Binary representation of "ADD" program in memory.

#### **Explanation**

Since the LDAA instruction is located at address 0000, this address must appear on the address bus for LDAA to be fetched. The PC is

Fig. 1-6. Hexadecimal representation of "ADD" program in memory.

set to the beginning address of our program, 0000 in this case. Since program execution begins at address 0000, the 6800 expects to find an instruction op code there and not data. If data is stored there, it is treated as an instruction op code. The CON (controller/sequencer) section of the 6800 then enables the PC to transfer its count to the MAR (memory address register). Immediately after the transfer, the PC is clocked and its count is incremented by one. The MAR is then

Fig. 1-7. LDA fetched and decoded.

enabled to transfer 0000 to the external memory. When memory location 0000 is accessed, its contents (86) are placed onto the data bus. This information is received by the DR (data register) then transferred to the ID (instruction decoder) for interpretation (decoding). Once the instruction is decoded, the CON provides the proper signals to execute the instruction. Observe the present register contents of the address section (Fig. 1-7). The PC contains 0001, which is the next memory location to be accessed. The MAR contains 0000, which is the address of the present memory location being accessed.

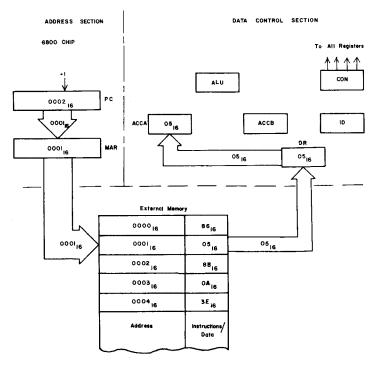

#### Figure 1-8

The operand (05) for the first instruction is fetched and loaded into accumulator A.

#### Explanation

The program count (0001) is transferred to the MAR and the PCs count is incremented. The MAR then places 0001 onto the address

Fig. 1-8. LDA execution.

bus to be transferred to external memory. Memory location 0001 is accessed and its contents are placed on the data bus. The DR receives 05 and loads it into accumulator A.

How did the DR know that its incoming information was an operand and not another instruction to be decoded?

After the LDA instruction was decoded, the CON signaled the other registers that the byte of information in the next memory location was an operand to be loaded into accumulator A.

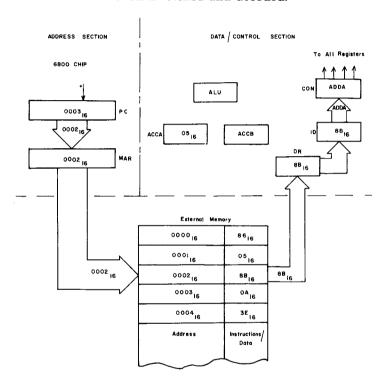

Figure 1-9

The ADDA instruction is fetched and decoded.

Fig 1-9. ADDA fetched and decoded.

#### Explanation

Address 0002 is placed on the address bus and the PC is incremented as before. The op code 8B is then accessed and placed on the data bus. The DR receives the instruction and passes it to the ID for decoding. The CON section then signals the other registers that the *next* byte in memory is an operand to be added to the contents of accumulator A and the sum is to be stored *back* into accumulator A.

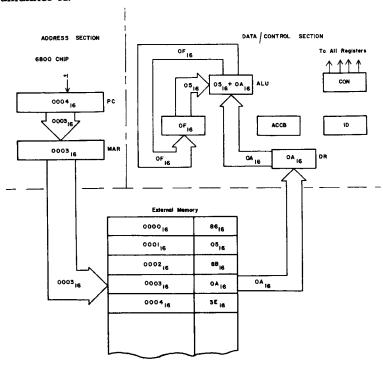

#### Figure 1-10

The value 0A is added to 05 with the results being placed in accumulator A.

Fig. 1-10. ADDA execution.

#### Explanation

Address 0003 is placed on the address bus as before and the operand 0A is accessed and placed on the data bus. The DR sends 0A to the alu. At about the same time, the CON section indicates to accumulator A that it is to send its contents to the alu. The alu then adds the two operands and places the result (0F) back in accumulator A. We will see later that once the result of an operation is in one of the accumulators, it can then be stored in memory, used in another operation, or transferred to an i/o device.

#### Figure 1-11

The WAIt instruction is fetched and executed.

Fig. 1-11. WAI fetched and executed.

#### Explanation

The instruction is accessed and decoded as before. The CON section indicates to the other registers that they are to wait or halt operation until further notice. Note that the result of the addition, 0F, remains in accumulator A (ACCA).

#### **REVIEW QUESTIONS**

- 1. What is a digital computer?

- 2. What number system does a digital computer utilize?

| 3. What is meant by base 10, base 2, base 16?                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| 4. Define the following terms: a. bit                                                                                                        |

| b. byte                                                                                                                                      |

| c. word                                                                                                                                      |

| 5. Which of the following is a byte? a. 1101                                                                                                 |

| b. 1101111                                                                                                                                   |

| c. 11011111                                                                                                                                  |

| d. 1000101011100111                                                                                                                          |

| 6. State the difference between a microprocessor and microcomputer.                                                                          |

| 7. What is meant by the term LSI?                                                                                                            |

| <ol> <li>Identify the following instructions as to whether they are binary code, hexadecimal code, or mnemonic code.</li> <li>WAI</li> </ol> |

| b. 11010011 <sub>2</sub>                                                                                                                     |

| c. 1101 <sub>16</sub>                                                                                                                        |

| d. LDA                                                                                                                                       |

| e. 1101 <sub>2</sub>                                                                                                                         |

| f. OFC9 <sub>16</sub>                                                                                                                        |

| 9. State the difference between RAM and ROM.                                                                                                 |

|            | b. TRS-80                                                                                                        |

|------------|------------------------------------------------------------------------------------------------------------------|

|            | с. 8080                                                                                                          |

|            | d. Z-80                                                                                                          |

| 11.        | What is meant by a chip family?                                                                                  |

|            |                                                                                                                  |

| 12.        | The 6800 uses abit data bus.                                                                                     |

| 13.        | The PC is abit counter.                                                                                          |

| 14.        | The MAR is a register.                                                                                           |

| 15.<br>16. | The performs all arithmetic and logic operations.  The 6800 contains how many accumulators? What are they named? |

| 17.        | Instructions can be bytes in length (how many?).                                                                 |

|            | The 6800 is capable of addressing memory locations.                                                              |

|            | The results of an arithmetic or logic operation are always placed in the                                         |

|            | <del></del>                                                                                                      |

| 20.        | With reference to the instruction being executed, the PC always contains                                         |

|            | the address of the program instruction.                                                                          |

| 21.        | A synonym for decoding is                                                                                        |

|            | ANOWERO                                                                                                          |

|            | ANSWERS                                                                                                          |

| 1.         | A computer that utilizes on/off states (binary) to represent numbers and make decisions.                         |

| 2.         | Binary, base 2.                                                                                                  |

10. Which of the following is a microcomputer system? a. 6800

- 3. Base 10 means decimal number system.

- Base 2 means binary number system.

Base 16 means hexadecimal number system.

- 4. a. A binary digit (1 or 0).

- b. 8 bits.

- c. Any number of bits, depending on how it's used.

- 5. c.

- A microcomputer is a fully operational digital computer that is based on a microprocessor.

- 7. Large Scale Integration—500-20,000 transistors and associated components per chip.

- 8. a. mnemonic

- b. binary

- c. hexadecimal

- d. mnemonic

- e. binary

- f. hexadecimal

- 9. RAM is random access memory (ROM is read-only memory).

- 10. TRS-80

- Generally, a group of chips designed to be compatible with a specific microprocessor chip.

- 12. 8

- 13. 16

- 14. storage or buffer, 16-bit

- 15. arithmetic logic unit (alu)

- 16. Two-ACCA and ACCB.

- 17. one, two or three

- 18. 65,536<sub>10</sub> (64K)

- 19. accumulator

- 20. next

- 21. interpret

## Heath ET3400 and Motorola MEK6800D2 Microcomputer Learning Systems

#### INTRODUCTION

In the chapters that follow, the Heath ET3400 or Motorola MEK-6800D2 learning systems will be used to demonstrate the concepts of microcomputer programming and interfacing. This chapter will familiarize you with the layout of each system and prepare us to use them properly to perform the experiments. It is assumed that the microcomputer system that will be used has already been properly assembled and tested and is in satisfactory working order. The programming experiments are designed to be used on either system. However, the interfacing experiments in Chapters 6 through 9 are only designed for the Heath ET3400 system. The interfacing experiments cannot be easily performed on the Motorola MEK6800D2 system since the data, address, and control signals are not made conveniently available and no solderless breadboarding region is supplied.

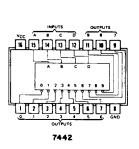

In order to complete all of the interfacing experiments, the following parts must be available in addition to the basic ET3400 training system:

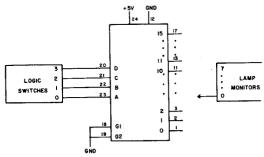

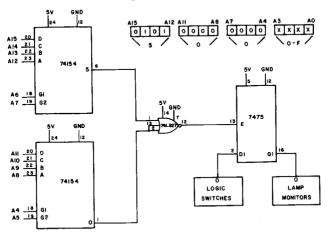

One 7400 digital IC (2-bit NAND—Heath #443-1 One 74LS30 digital IC (8-bit NAND)—Heath #443-732 One 74LS27 digital IC (3-bit NOR)—Heath #443-800 One 7475 digital IC (Dflip-flop) One 6820 or 6821 PIA-Heath #483-843

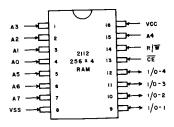

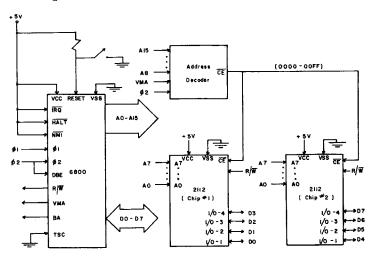

Two 2112 256  $\times$  4 R/W memory chips—Heath #443-721

One TIL-312 7-segment display-Heath #411-831

One solderless connector block—Heath #432-875

Four push-button switches-Heath #64-724, 64-725, 64-726, 64-727

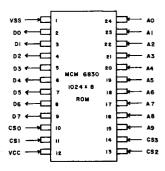

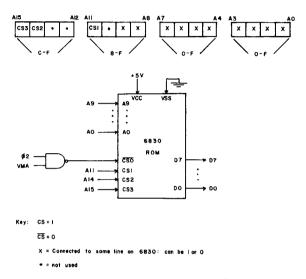

One Motorola MCM6810 128 ×8 R/W memory chip

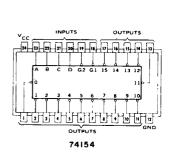

Two 74154 one-of-sixteen decoders

Five 1000-ohm 4-watt resistors

No. 20-No. 22 wire cut to 3", 6", and 9" lengths (approximately 25 of each length)

#### **OBJECTIVES**

At the end of this chapter you will be able to do the following:

- Describe the characteristics of each major functional area of the learning system.

- Identify the input/output parts of the system.

- For the ET3400, demonstrate the operation of the eight binary switches and LEDs.

- For the ET3400, demonstrate the operation of the DO, EXAM, FWD, AUTO, BACK, CHAN, SS, ACCA, ACCB, and PC keys on the keyboard.

- For the MEK6800D2, demonstrate the operation of the N, V, M, E, R, anid G keys on the keyboard.

- Load and execute a simple microcomputer program on each system.

- Trace a program through the 6800 chip with each system.

#### **HEATH ET3400 MICROCOMPUTER LEARNING SYSTEM**

The ET3400 is truly a *student-oriented* learning system. It is well designed to provide the student with an efficient learning experience in microcomputer architecture, programming, and interfacing. And yet, it is a powerful and versatile microcomputer. The system can be purchased from Heath in kit form for under \$200.

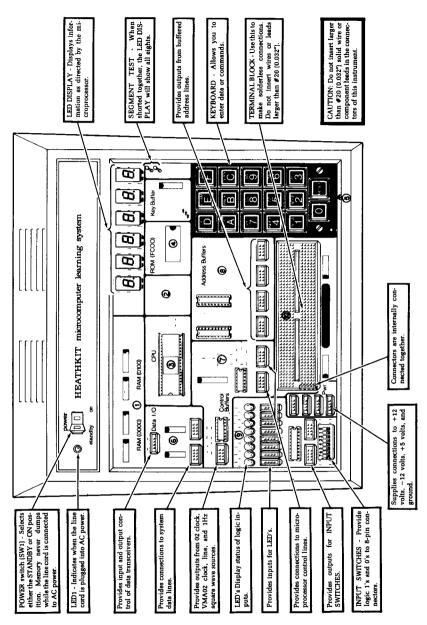

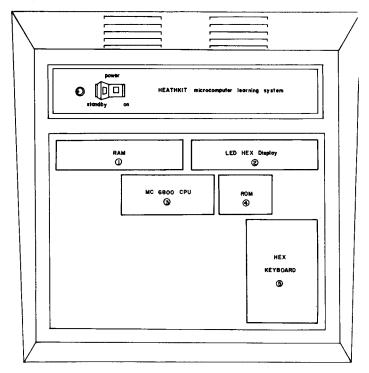

A composite pictorial view of the learning system is shown in Fig. 2-1. This system can be broken down into two major areas as follows:

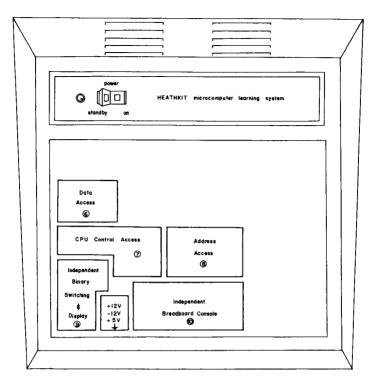

- 1. Those regions used for actual computation, memory, and i/o (Fig. 2-2).

- 2. Those regions which allow us to access different parts of the system and to breadboard external circuits to the system (Fig. 2-3).

Courtesy Heath Co.

Fig. 2-1. Pictorial view of Heath ET3400 Microcomputer Learning System.

#### **Functional Operating Regions**

Refer to Figs. 2-1 and 2-2 which use numbered references. An explanation of each number reference follows.

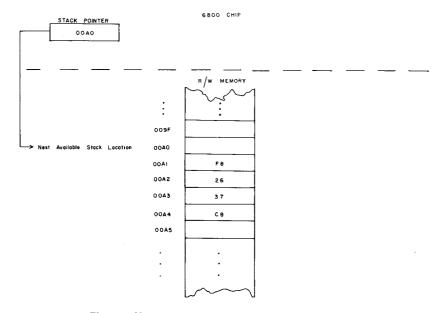

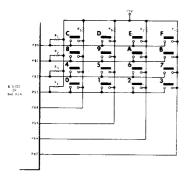

1. RAM—Random Access or read/write Memory. This is the region where information can be stored and retrieved. It consists of 2 pairs of RAM chips. Each pair consists of two 256 by 4-bit

Fig. 2-2. Functional operating regions of Heath ET3400 Microcomputer Learning System.

(256×4) chips, which means that 256 4-bit words per chip or 256 8-bit words for each pair of chips can be stored. Since we have 2 pairs, the system is capable of storing 512 8-bit words in RAM. One pair comprises memory locations 0000<sub>16</sub> through 00FF<sub>16</sub> (256 locations) and the other pair starts at memory location 0100<sub>16</sub> and ends with 01FF<sub>16</sub> (256 locations) for a total of 512 8-bit read/write memory locations.

Fig. 2-3. Access and breadboarding regions of Heath ET3400 Microcomputer Learning System.

- LED Hex Display—This is an output display that consists of six 7-segment LED displays. The system will display information on these displays in hexadecimal as directed by the microprocessor.

- 3. MC6800 CPU—The microprocessor chip which performs all computation and control functions.

- 4. ROM-Read-Only Memory is a memory chip that has been preprogrammed to make the system much more convenient to use. It contains a program which allows the use of hex rather than binary. It also permits you to do many other convenient things that will become valuable as the experiments are performed. This chip contains 1024 8-bit memory locations which begin at address FC00<sub>16</sub>. This area of memory cannot be used for your program.

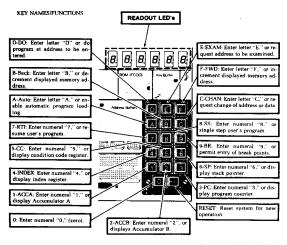

- 5. Hex Keyboard—Allows you to enter data or commands in hexadecimal. Each key except for 0 and RESET is a dual-function key. The functions of each key are described in Fig. 2-4.

Courtesy Heath Co.

Fig. 2-4. Keyboard layout and key functions of Heath ET3400 Microcomputer Learning System.

#### **Access and Breadboarding Regions**

Refer to Figs. 2-1 and 2-3 using the numbered references.

- 6. Data Access—At the top of this region is a connector block for data i/o control. At the bottom of the region are eight dual-inline solderless breadboard sockets for access to each of the eight data bus lines (D0-D7).

- 7. CPU Access—The three solderless connector blocks in this region provide a direct connection to the various control pins on the 6800. More will be said about these later.

- 8. Address Access—This area consists of 16 dual-inline solderless breadboard sockets for access to each of the 16 address bus lines (A0-A15).

- 9. Binary Switches and Displays—This section is independent from the other regions of the system. It consists of eight microswitches (0-7) to provide logic ones and zeros to the dual-inline eight-pin connectors located just above the switches. It also consists of eight LED display indicators (0-7) to monitor logic status, which are connected through the dual-inline eight-pin connectors located just below the LEDs.

- 10. Breadboard Console—The breadboard is also independent from the other regions of the system. It is designed to accommodate the many experiments that will be performed in subsequent chapters. Integrated-circuit chips, resistors, capacitors, and wires

can all be connected in the solderless breadboard sockets. Do not use wires or leads larger than AWG#20 (.032").

#### MOTOROLA MEK6800D2 EVALUATION KIT

The MEK6800D2 evaluation kit, marketed by Motorola, is a 6800-based system very much like the Heath ET3400 system. It is designed for the engineer, technician, or experimenter who wants to familiarize himself with the 6800 CPU. The system is not as well documented as the Heath ET3400 and the individual is more or less left "hanging" as how to program and interface it. By following this and subsequent sections, you should become much more familiar with the use of the MEK6800D2 system. The kit is available from Motorola for less than \$200 with a student discount.

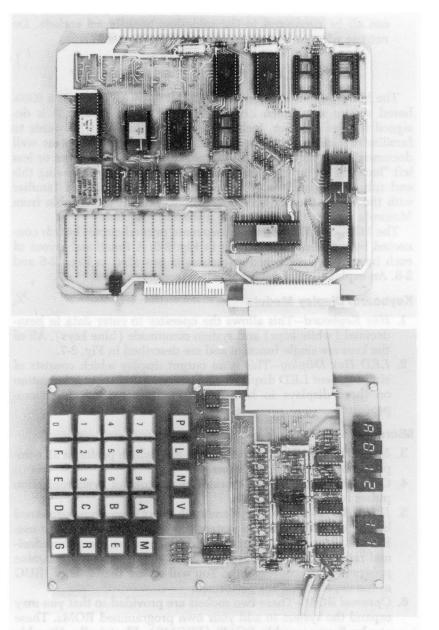

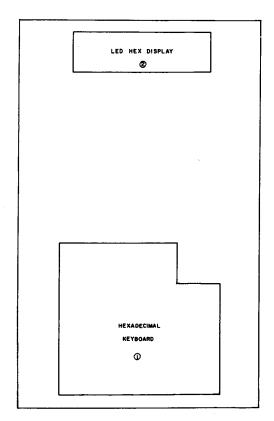

The MEK-6800D2 consists of two main printed-circuit boards connected by a flex cable as shown in Fig. 2-5. A functional layout of each board with numbered references is provided in Figs. 2-6 and 2-8. An explanation of each number reference follows.

#### **Keyboard/Display Module**

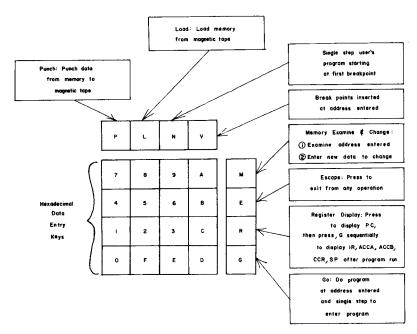

- 1. Hex Keyboard—This allows the operator to enter data in hexadecimal (white keys) and system commands (blue keys). All of the keys are single function and are described in Fig. 2-7.

- LED Hex Display—This is an output display which consists of six 7-segment LED displays. The system will display information on these displays in hexadecimal as directed by the microprocessor.

#### Microcomputer Module

- 3. MC6800 CPU—The microprocessor chip which performs all computation and control functions.

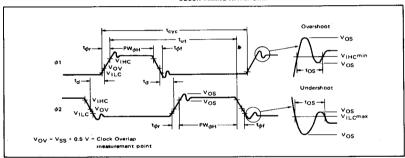

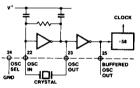

- 4. Clock—A square-wave generator that provides synchronization pulses for the 6800 CPU.

- 5. IBUG ROM—Read-Only Memory that has been preprogrammed by Motorola to make the system much more convenient to use. For one, it contains a program which allows the use of hexadecimal rather than binary. It also allows you to enter and examine programs more conveniently. You will realize the value of JBUG as the experiments are performed.

- 6. Optional ROM-These two sockets are provided so that you may expand the system to add your own programmed ROMs. These can be Programmable ROMS (PROMS), Electrically Alterable ROMS (EAROMS), or Erasable PROMS (EPROMS).

Courtesy Motorola Semiconductor Products Inc.

Fig. 2-5. Pictorial view of Motorola MEK6800D2 Evaluation Kit.

Fig. 2-6. Keyboard/display module of Motorola MEK6800D2 Evaluation Kit.

- 7. RAM—Random-Access or read/write Memory. This is the region where information can be stored and retrieved. The basic kit consists of three RAM chips. Each chip is a 128 by 8-bit (128×8) chip; which means that 128 8-bit words can be stored per chip. Two of the chips are available to the user, with the third chip being reserved for use by the JBUG ROM program. Therefore, with the two chips provided for the user, 256 8-bit words can be stored in RAM.

- 8. Optional RAM—These two sockets are provided so that the "onboard" RAM capability may be expanded to 512 bytes.

- ACIA—Asynchronous Communications Interface Adapter. The basic function of ACIA is to provide serial/parallel data conversions. It will take parallel data bus information and convert it to serial data to be transmitted to some i/o device. It will also ac-

cept serial data from an i/o device and convert it to parallel data to be used by the CPU. The main applications of the ACIA would be in interfacing the MEK6800D2 system to some serial device such as a cassette, teletype, printer, or telephone line (modem).

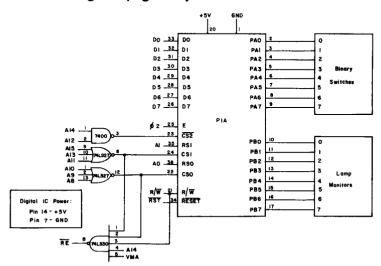

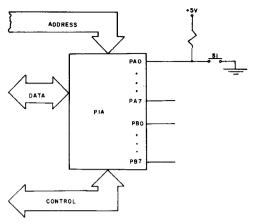

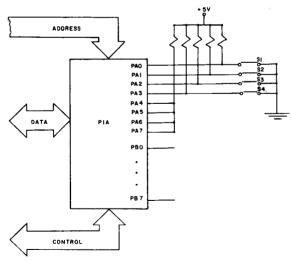

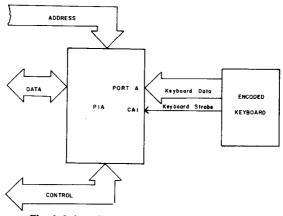

10. PIA—Peripheral Interface Adapter. This is a programmable device which is used to provide basic input and output interface

Fig. 2-7. Keyboard layout and key functions for Motorola MEK6800D2 Evaluation Kit.

for 8 bits of parallel data. Each PIA contains two 8-bit channels (ports) which can be used for either input or output. The PIA in the upper right corner of Fig. 2-8 is used by the MEK6800D2 system to interface the keyboard/display module to the microcomputer module. The PIA below this one is available for parallel interfacing. More information about this device is contained in Chapters 8 and 9.

- 11. RESET-Reset system for new operation.

- 12. The large open area in the lower right-hand corner of Fig. 2-8 is provided for user-designed circuitry to be added to the system.

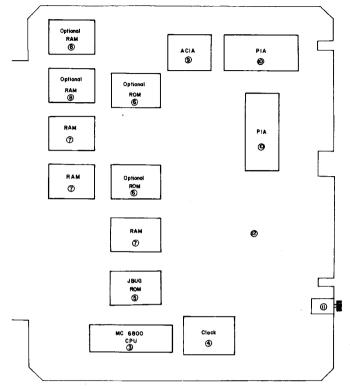

Fig. 2-8. Microcomputer module of Motorola MEK6800D2 Evaluation Kit.

#### **EXPERIMENT INSTRUCTIONS AND FORMAT**

The instructions for each experiment are presented in the format described below.

# **Purpose**

The material under this category states the intended purpose of the experiment. Keep this purpose in mind as you conduct the experiment.

# **Equipment**

This category will list the equipment required to complete the experiment including any external integrated circuits, transistors, resistors, capacitors, etc. There will be two listings: one of the equipment required for the Heath ET3400 trainer and the other of the equipment required for the Motorola MEK6800D2 system.

# **Schematic Diagram**

A schematic diagram of the completed circuit to be used in the experiment is provided. The user should make an effort to follow the diagram and understand the circuit before doing the experiment.

# **Program**

The hexadecimal microcomputer program to be loaded into RAM at the indicated memory addresses will be provided.

#### Procedure

A sequential step-by-step procedure for completing the experiment will be provided. In some cases, the procedure will be divided into two sections, one for the ET3400 trainer and the other for the MEK-6800D2 trainer.

#### **Conclusions**

Space will be given at the end of each experiment to form conclusions. Questions will be asked in an attempt to guide your thinking. Try to sincerely answer these questions. Ask yourself: What concepts are being demonstrated?

#### **EXPERIMENT 2-1**

# **Purpose**

To provide power to the microcomputer system and prepare the system for operation.

# **Equipment**

ET3400

MEK6800D2 5-volt dc power supply

#### **Procedure**

ET3400

# Step 1

Plug in the system and turn the power switch to "on."

# Step 2

Press the RESET button on the keyboard and the hex display should indicate "CPU UP."

Answer the questions at the end of this experiment and draw your conclusions.

#### MEK6800D2

# Step 1

Apply +5 volts dc to point A of the J1 connector located on the microcomputer module.

# Step 2

Apply ground ( $\stackrel{\perp}{=}$ ) to point  $\overline{C}$  of the J1 connector located on the microcomputer module.

# Step 3

Press the RESET button (S1) located on the microcomputer module. The hex display should show a dash "—" on the first 7-segment LED (U1). All the other displays should be blank.

# Step 4

Answer the questions at the end of this experiment and draw your conclusions.

# Conclusions

Was the proper display achieved? If not, why?

If the proper display was not achieved, repeat the procedure. If it fails again, test and troubleshoot the system until this experiment can be successfully completed.

For the Heath ET3400, what caused the display to show "CPU UP" after the RESET button was pressed?

For the Motorola MEK6800D2, what caused the display to show "- " after the RESET button was depressed?

#### **EXPERIMENT 2-2**

#### **Purpose**

To demonstrate the method of program entry into RAM.

#### **Equipment**

ET3400

MEK6800D2 +5-volt dc power supply

# **Program**

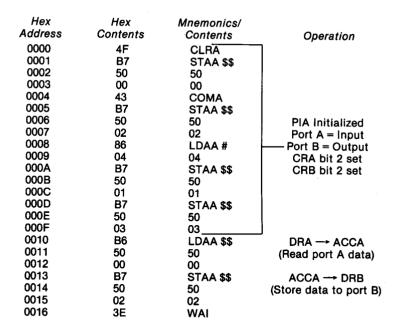

| Hex<br>Address | Hex<br>Contents | Mnemonics/<br>Contents | Operation                        |

|----------------|-----------------|------------------------|----------------------------------|

| 0000           | 86              | LDA                    |                                  |

| 0001           | 05              | 05                     | 05 → ACCA                        |

| 0002           | 8B              | ADDA                   |                                  |

| 0003           | 0A              | 0A                     | $(05 + 0A) \longrightarrow ACCA$ |

| 0004           | 3E              | WAI                    | Stop                             |

#### **Procedure**

ET3400

# Step 1

Press RESET then AUTO. The display should show "----Ad."

# Step 2

Press 0000 for the first address then 86 for the first op code. The display should now indicate "0001". Note that it has automatically incremented to the next address.

# Step 3

Enter the operand-05.

# Step 4

Continue to enter the rest of the program.

# Step 5

Press RESET. The program is now entered in RAM and the display should indicate "CPU UP."

Answer the questions at the end of this experiment and draw your conclusions.

#### MEK6800D2

### Step 1

Press the RESET button on the microcomputer module board. The display should show "\_\_\_\_\_."

#### Step 2

Enter 0000 for the first address then press M.

# Step 3

Enter 86 for the first op code. The display should now show "0000 86."

# Step 4

Press G and enter 05 for the operand. The display should now show "0001 05." Note that the address incremented by one when the G key was pressed.

# Step 5

Press G and enter the next op code and continue until the entire program is loaded.

# Step 6

Press E. The program is now entered in RAM and the display should indicate "- ."

# Step 7

Answer the questions at the end of this experiment and draw your conclusions.

#### **Conclusions**

Why did you have to enter the first address and none of the other addresses?

What caused the address to automatically increment?

Why did you have to RESET the system after program entry?

#### **EXPERIMENT 2-3**

# **Purpose**

To examine RAM contents, specifically the program entered in Experiment 2-2. Also, to change the contents of a memory location.

#### **Equipment**

| ET3400 | MEK6800D2               |

|--------|-------------------------|

|        | +5-volt dc power supply |

#### **Program**

| Hex<br>Address | Hex<br>Contents | Mnemonics/<br>Contents | Operation        |

|----------------|-----------------|------------------------|------------------|

| 0000           | 86              | LDA                    |                  |

| 0001           | 05              | 05                     | 05 → ACCA        |

| 0002           | 8B              | ADDA                   |                  |

| 0003           | 0A              | 0A                     | (05 + 0A) → ACCA |

| 0004           | 3E              | WAI                    | Stop             |

#### **Procedure**

ET3400

# Step 1

Enter the above program into RAM. Press RESET and then EXAM. The display should show "----Ad."

# Step 2

Press 0000 for the first address of your program. The display should show the contents of memory location 0000 which should be 86.

# Step 3

Press FWD and the display should show the contents of memory location 0001.

# Step 4

Continue to press FWD to examine each subsequent memory location. Verify that your program entry was correct.

Now suppose we wish to change memory location 0003 from 0A to 0B. Press EXAM and then the address to be changed which is 0003.

#### Step 6

Press CHAN and then the new contents, 0B.

# Step 7

Re-examine the program to verify the change has been made.

#### Notes:

- 1. You may examine any specific location by pressing EXAM and then the address.

- While examining a program, a change may be made at any time by pressing CHAN and then entering the new contents.

- 3. You may also backstep through the program with the "BACK" key.

# Step 8

Answer the questions at the end of this experiment and draw your conclusions.

# MEK6800D2

# Step 1

Enter the program into RAM. Press the E key and then 0000 for the first address in your program.

# Step 2

Press M and the display should show the contents of address 0000 which should be 86.

# Step 3

Press G and the display should show the contents of memory location 0001.

# Step 4

Continue to press G to examine each subsequent memory location. Verify your program entry was correct.

Now suppose we wish to change memory location 0003 from 0A to 0B. Press E and then the address to be changed which is 0003.

#### Step 6

Press M and then the new contents-0B.

#### Step 7

Re-examine the program to verify the change has been made

#### Notes:

- 1. You may examine any specific memory location by pressing E and then the address followed by M.

- 2. While examining a program, a change my be made at any time by simply entering the new contents.

# Step 8

Answer the questions at the end of this experiment and draw your conclusions.

#### **Conclusions**

When should a program be examined?

With the Heath ET3400 system, what are the relationships between the EXAM and FWD keys?

With the Motorola MEK6800D2 system, what are the relationships between the M and G key?

With the Heath ET3400, what is the function of the BACK key?

#### **EXPERIMENT 2-4**

#### **Purpose**

To execute a simple program and verify its results. Also, to examine the program counter and accumulator contents at each step of a program.

# Equipment

ET3400 MEK6800D2 +5-volt dc power supply

# Program

| Hex<br>Address | Hex<br>Contents | Mnemonics/<br>Contents | Operation        |

|----------------|-----------------|------------------------|------------------|

| 0000           | 86              | LDA                    | •                |

| 0001           | 05              | 05                     | 05 → ACCA        |

| 0002           | 8B              | ADDA                   | 33 713 671       |

| 0003           | 0A              | 0A                     | (05 + 0A )→ ACCA |

| 0004           | 3E              | WAI                    | Stop             |

#### **Procedure**

ET3400

# Step 1

Enter and examine the above program for proper entry. Always examine your program after entry.

# Step 2

Press RESET and then DO. The display should show "----do."

# Step 3

Enter the starting address of your program (0000). The display should go blank, indicating that your program has been executed.

# Step 4

The program adds 05 + 0A and stores the results (0F) into ACCA. Press RESET then ACCA and observe the results. The display should indicate "Acca 0F." If it does not, re-examine your program, make any required changes, re-execute and verify the proper results in ACCA.

Now you will step through the program, observing the contents of PC and ACCA at each step.

#### Step 6

Press PC and change its contents to 0000 by using the CHAN key. This tells the computer to start single stepping at 0000.

# Step 7

Press SS. The display should show the next command instruction which is 8B located at address 0002.

# Step 8

Press ACCA and observe its contents. It should be 05 since to this point you have only executed the first instruction which loads 05 into accumulator A.

# Step 9

Press PC and observe its contents. It should be 0002 which is the address of the next instruction to be executed.

# Step 10

Press SS. This display should indicate "0004 3E" which is the next command instruction to be executed. You have just executed the ADDA instruction.

# Step 11

Press ACCA and observe its contents. This should be 0F since 0A has been added to 05, with the sum (0F) stored in accumulator. A.

# Step 12

Press PC and note that it contains the address of the next instruction to be performed (0004).

# Step 13

Press SS and note that the display does not change. This is because the next instruction was a stop command and control of the system by the SS key is stopped at this point.

# Step 14

Change memory location 0003 to 0B and repeat the above procedure. This time, the result in accumulator A should be 10.

Answer the questions at the end of this experiment and draw your conclusion.

#### MEK6800D2

#### Step 1

Enter and examine the program for proper entry. Always examine your program after entry.

#### Step 2

Press E and then enter the starting address of your program (0000).

# Step 3

Press G. The display should go blank, indicating that your program has been executed.

# Step 4

The above program adds 05 + 0A and stores the result (0F) into ACCA. To observe the contents of ACCA, press E then R, and then press the G key *twice* and observe the display. The display should show "0F." If it does not, re-examine your program, make any required changes, re-execute, and verify the proper results in ACCA.

# Step 5

Now we will step through the program, observing the PC and ACCA contents at each step. Press E to reset the system.

# Step 6

Enter the starting address of your program followed by V. This enters a "breakpoint" at address 0000, which allows you to start single stepping through the program at this point.

# Step 7

Press G. The program will Go to the first breakpoint and then stop. By pressing the G key two more times, you can display the contents of ACCA. It should be a random number since no data has been loaded into the accumulator at this point.

Now press the N key. This will single step the program and cause the first instruction to be executed. The display should show 0002 8B. The contents of the PC is 0002, which is the address of the next instruction to be performed.

# Step 9

Press the G key twice and observe the accumulator contents. It should be 05, since at this point we have only executed the first instruction which loads 05 into accumulator A.

# Step 10

Press N. This will single step the program again and cause the second instruction to be executed. The display should show 0004 3E. The contents of the PC is 0004, which is the address of the next instruction to be performed.

# Step 11

Press the G key twice and observe the accumulator contents. It should be 0F since 0A has been added to 05 with the sum stored in accumulator A. The N key can now be used to single step as many instructions as desired.

Note: If the E key is pressed at any time, the breakpoint will be removed. The breakpoint must be re-installed if it is desired.

# Step 12

Change memory location 0003 to 0B and repeat the above procedure. This time, the result in accumulator A should be 10.

# Step 13

Answer the questions at the end of this experiment and draw your conclusions.

#### Conclusions

In what part of the 6800 did the addition take place? Where was the sum stored?

Why would it not be advisable to use the accumulator as a permanent storage register? Where might it be better to store an operation result?

Why does the PC always indicate the address of the next instruction to be performed?

What controls the single-step routine of your trainer?

#### **EXPERIMENT 2-5**

#### **Purpose**

To store an operation result in memory.

#### Equipment

ET3400

MEK6800D2 +5-volt dc power supply

#### **Program**

| Hex<br>Address | Hex<br>Contents | Mnemonics/<br>Contents | Operation                |

|----------------|-----------------|------------------------|--------------------------|

| 0020           | C6              | LDB                    | w.                       |

| 0021           | 05              | 05                     | 05 → ACCB                |

| 0022           | СВ              | ADDB                   |                          |

| 0023           | 0A              | 0A                     | (05 + 0A) → ACCB         |

| 0024           | D7              | STAB                   | ( ,                      |

| 0025           | 50              | 50                     | ACCB + → M <sub>50</sub> |

| 0026           | . 3E            | WA1                    | Stop                     |

The above program loads ACCB with 05 then adds 0A to 05. The sum is placed in ACCB then the STAB stores the sum into memory location 50. (STAB means STore Accumulator B at the specified memory location.)

#### **Procedure**

ET3400

# Step 1

Enter the above program into memory beginning with address 0020.

# Step 2

Examine the program and make any required changes.

# Step 3

Execute the program. (Remember, the program begins at address 0020.)

Observe the contents of ACCA. It should be some random number or the result of the last experiment, since this program uses ACCB.

# Step 5

Observe the contents of ACCB by using the ACCB key. The display should be "ACCB 0F," indicating the sum of 05 + 0A.

# Step 6

The program should have stored this sum in memory location 50. Examine this memory location. The display should show "0050 0F."

# Step 7

Step through the program and observe the PC and ACCB contents at each instruction step. (Reference Experiment 2-4.)

# Step 8

Change the program to add  $44_{10} + 48_{10}$  and store the results at memory location  $252_{10}$ .

# Step 9

Execute the program and verify your results.

#### MEK6800D2

# Step 1

Enter the above program into memory beginning with address 0020.

# Step 2

Examine the program and make any required changes.

# Step 3

Execute the program. (Remember, the program begins at address 0020.)

# Step 4

Observe the contents of ACCA by pressing E, R, and then the G key twice. The display should indicate some random number since this program uses ACCB.

Observe the contents of ACCB by pressing the G key one more time. The display should be "0F", "indicating the sum of 05 + 0A.

NOTE: After pressing E and then R, the display will show the PC contents. Then, sequencing G twice will show ACCA contents. Sequencing G three times will show ACCB contents.

#### Step 6

The program should have also put this sum at memory location 50. Examine this memory location. The display should show "0F..."

#### Step 7

Step through the program and observe the contents of the PC and ACCB at each instruction step. (Reference Experiment 2-4.)

#### Step 8

Change the program to add  $44_{10} + 48_{10}$  and store the results at memory location  $252_{10}$ .

# Step 9

Execute the program and verify the results.

#### **Conclusions**

Why would you want to store the results of an operation in memory?

What would be the highest memory location available for storage with your system?

Was there any noticeable difference in using ACCB rather than ACCA? If so, what?

Can you think of a case where you might want to use both ACCA and ACCB in the same program? (Explain.)

#### **CHAPTER 3**

# 6800 Arithmetic, Logic, and Data-Handling Instructions

#### INTRODUCTION

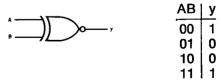

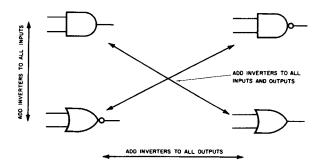

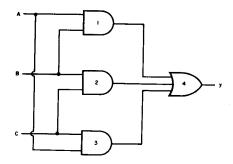

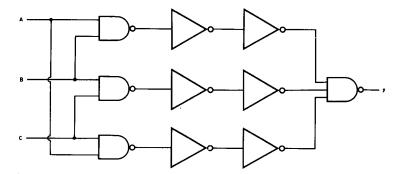

Now we are ready to begin studying the 72 fundamental instructions utilized by the 6800 microprocessor. These instructions, along with their various addressing modes, make up the total 6800 instruction set of 197 instructions. With this instruction set you will form programs that make the 6800 a very powerful microprocessor. These programs make up the software part of a microcomputer system. Software is what makes the system so flexible, since it takes the place of digital logic gates. Given a specific application involving a decision-making problem, a conventional digital design approach could be used. This design might consist of anywhere from one to one thousand digital logic gates. However, with a microprocessor-based design the logic gates are replaced with software instructions. Now suppose that you wish to change the application. In most cases, the conventional design would require a complete redesigning and rebuilding of the system. However, with the microprocessor-based design only the program needs to be changed to change the application. This flexibility at minimal cost is what has made the microprocessor so valuable.

The 6800 instruction set can be broken down into seven general categories as follows:

- 1. arithmetic

- 2. logic

- 3. data handling

- 4. data test

- 5. condition code

- 6. index register and stack pointer

- 7. jump and branch.

In this chapter we intend to discuss the first three categories in part. Since the 6800 chip uses binary data internally and the arithmetic instructions involve binary arithmetic, it might be helpful to review *Digital Computer Arithmetic* in Appendix B, prior to reading this chapter.

# **OBJECTIVES**

At the end of this chapter you will be able to do the following:

- Write a simple arithmetic or logic program for the 6800.

- Define Inherent, Immediate, Direct, and Extended Addressing.

- Know when to use or when not to use a particular addressing mode.

- Add, subtract, and perform logic operations on binary numbers the way the 6800 does.

- Interpret simple 6800 arithmetic and logic instruction mnemonic and op-code listings.

- Represent negative numbers using the twos-complement number code.

- Define a status byte and a mask byte.

- Explain how logical instructions can be used to determine the status of an external device.

- Explain how logical instructions can be used to determine any change in the state of an external device.

# 6800 DATA TRANSFER

# Load Accumulators (LDAA, LDAB)

As discussed in Chapter 1, the 6800 has two 8-bit accumulators, A and B. These accumulators are used as temporary storage registers for operands and operation results. The LDAA (LoaD Accumulator A) and LDAB (LoaD Accumulator B) instructions allow you to load data into either accumulator immediately from the byte that immediately follows the instruction or directly from a memory location. The experiments in Chapter 2 used this instruction to load data

immediately; that is, the data to be loaded followed the instruction as an operand. This is referred to as immediate addressing. Another way to load data into the accumulator is from a memory location. When this method of loading the accumulator is desired, the address of the memory location that contains the operand must be specified. In this case, the byte or bytes that follow the LDA instruction will represent an address rather than the actual data that is to be used in the operation. This mode is referred to as direct addressing. When an address is specified following an instruction, it can be either one or two bytes depending upon the type of addressing that is to be used. A one-byte address may be used to specify any address from location  $00_{16}$  to  $FF_{16}$  or a two-byte address may be used to specify an address from locations  $0000_{16}$  to  $FFFF_{16}$ . When two address bytes

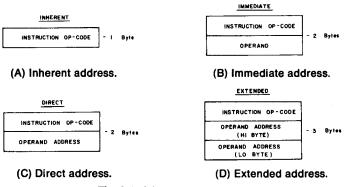

Fig. 3-1. Addressing modes.

are used following an instruction, the mode is referred to as extended addressing. When extended addressing is used, the first byte is called the high address byte, representing the upper eight bits of an address, and the second byte is referred to as the low address byte, representing the lower eight bits of an address. The instruction formats for the above addressing modes are shown in Fig. 3-1.

# Question

How does the 6800 know which type of addressing is being used?

#### Answer

There are three separate op codes for the load accumulator instruction to designate either the immediate, direct, or extended mode of addressing. For example, the LDAA instruction utilizes the following op codes:

# LDAA (LoaD Accumulator A) $M_x \rightarrow ACCA$

The byte immediately following the op code is Immediate

the operand to be loaded into ACCA. 86

DATA

Direct The byte following the op code is the address of 96

the operand to be loaded into ACCA (No HI

LO ADDR ADDR)

LO ADDR

Extended The next two bytes is the address of the operand

**B6** to be loaded into ACCA.

HI ADDR

The same is true for the LDAB instruction.

#### LDAB (LoaD Accumulator B) $M_x \rightarrow ACCB$

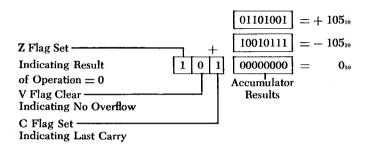

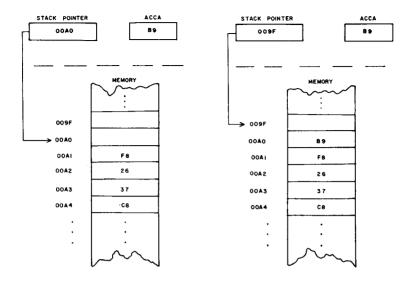

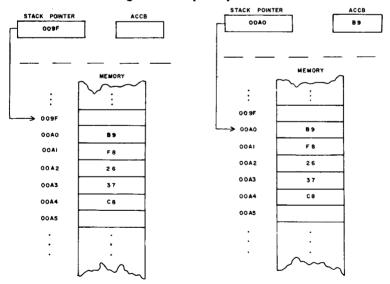

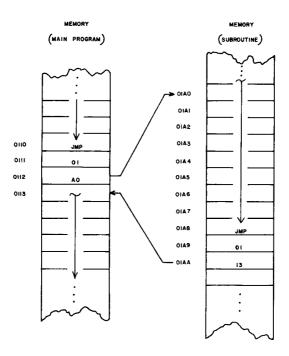

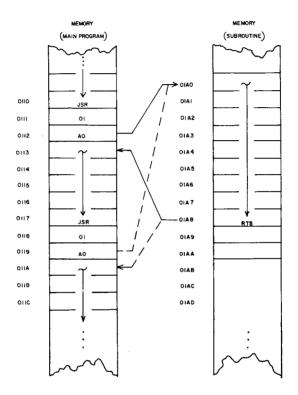

Immediate The byte immediately following the op code is C6